piotro.eu

Blog

About me

Projects

Research

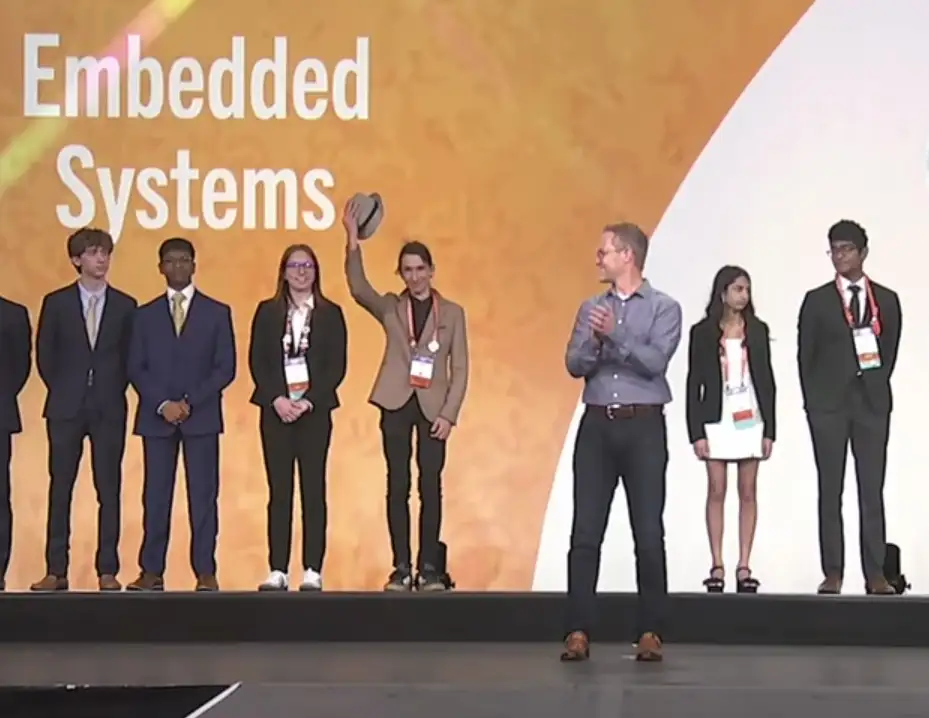

Achievements

Contact

GitHub

piotro.eu

Blog

About me

Projects

Research

Achievements

Contact

GitHub

I'm piotro

Piotr Węgrzyn

My name is Piotr Węgrzyn. I'm mainly interested in low-level stuff (especially lower than assembly :)), and everything at the boundary of programming and electronics.

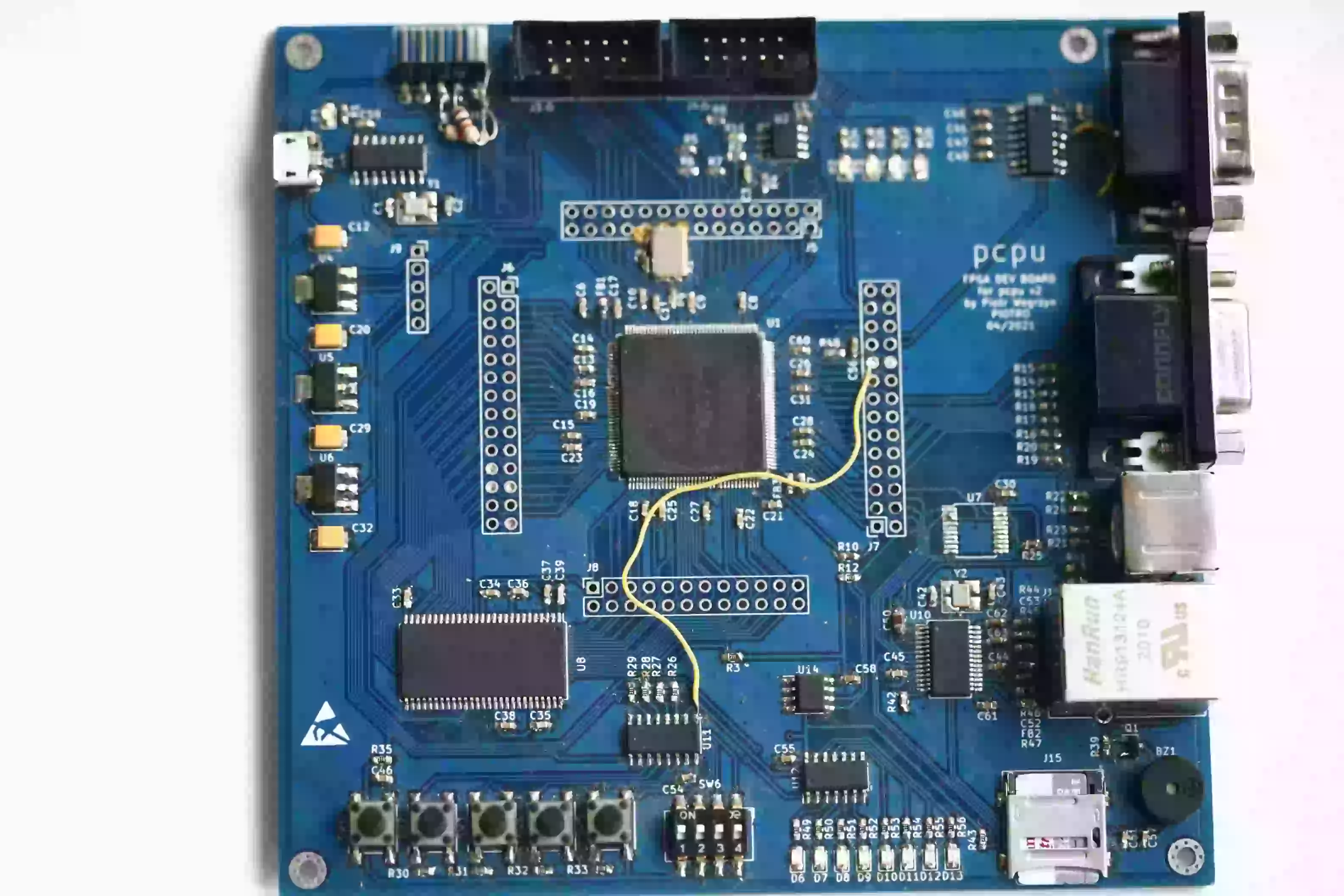

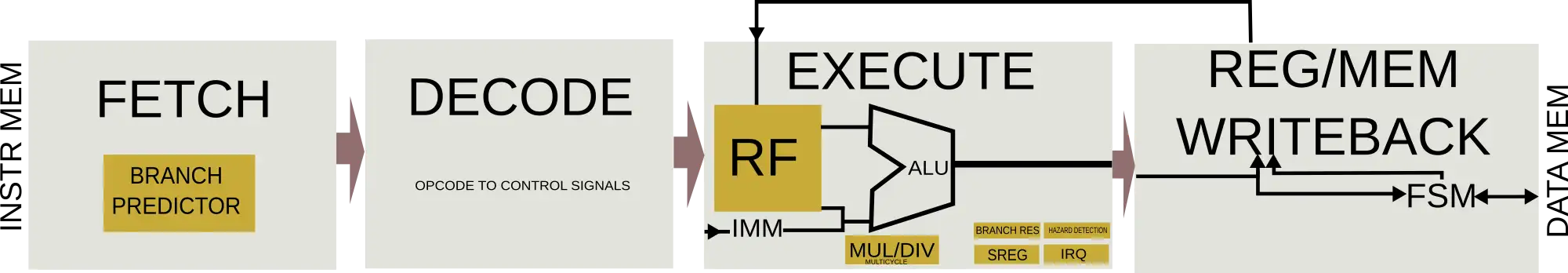

My biggest project so far is the PCPU - processor that I created completely from scratch, from the instruction set, through architecture, compilers, custom dev board, FPGAs, own operating system, and multiple re-designs, finally achieving manufactured silicon integrated circuit. I was doing this project throughout my high school, with no previous background, learning everything on my errors.

I'm currently a student at the University of Wrocław, where I'm participating in the Coreblocks project, creating Out-of-Order processor generator. I'm also a president of "Continuum" Students Association, promoting electronics and mechanics in our Institute of Computer Science.

I'm keeping electronics and radio as a hobby, doing some interesting projects from time to time. I enjoy sailing, climbing, old technology, sometimes photography and drawing too.

I love open source software and unix based systems. I'm also interested in networking aspects and servers - this website is (of course) proudly self-hosted.

You could have heard about me from the mentioned PCPU project, my research work, competitions, or maybe my talks.

~ Go your own route and never give up!

Student at the University of Wrocław

Graduated: XIV High School Wrocław

My research work:

I'm one of the main developers of the Coreblocks project. It is an open source Out-of-Order RISC-V processor generator. We are working on it with Kużnia Rdzeni (Coreforge) academic research group at the University of Wrocław.

Coreblocks is created in a very modular way using our Transcatron library for Amaranth HDL. It supports many configuration options and with its modular design is a great option for performing research. Long term goal is to approach the state of the art of current processors. It currently supports RV32IMCB architecture. It is fully functional and can be easily used on FPGAs with LiteX SoC generator.

The only similar projects are BOOM core from the University of California and XiangShan from the Chinese Academy of Sciences, our being the most customizable one (work is still in progress, while it is perfectly usable for simpler targets for now). We are currently focusing on implementing previously simplified, performance improving elements and extending functionality to more extensions, and integrating with more tools and systems.

Some parts that I implemented in the project are: exception and miss-speculation internal core flushing; interrupt controller; control and status registers (CSR); immediate support; wishbone bus; porting LiteX; and parts of CI testing

My (loosely defined) goal in the project is to make it capable of running Linux. Currently, I'm working/planning to work on: checkpointing; non-blocking coherent data cache; multi-core configurations; chipyard support; porting Zephyr RTOS; and RISC-V user and supervisor mode

Make sure to check it out! Coreblocks @ GitHub

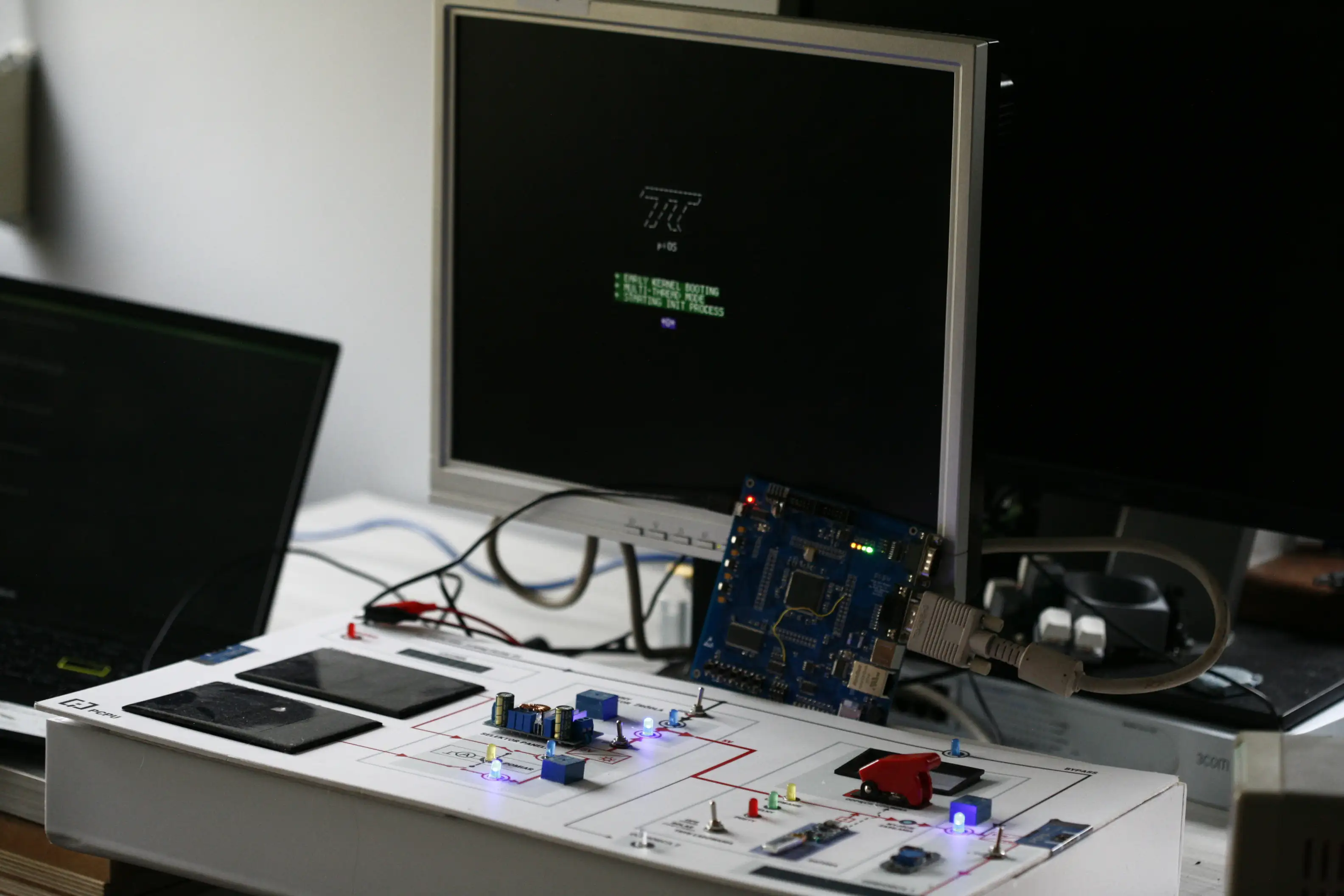

PCPU is a project that I created while studying in high school. It was entirely driven by my curiosity - I started working on it with no prior knowledge in this field. I had to learn everything myself, on my own errors, and it was really hard... While designing every detail of the project, I tried to learn and take the best from already existing solutions, mix that with some of my ideas, and create something interesting and unique.

During my work on the PCPU I also got interested in other interconnected fields of study and created other related projects. My work included:

Finally, it was an awesome adventure, where I started with the simplest processor design on paper, and ended up hand-crafting my very own complete computer

More details on the entire project are available in the projects section or my talks

About interesting aspects of 4 year history creating the full PCPU project [best rated talk]

Shortened version of the talk above (without a section about silicon), video recording available

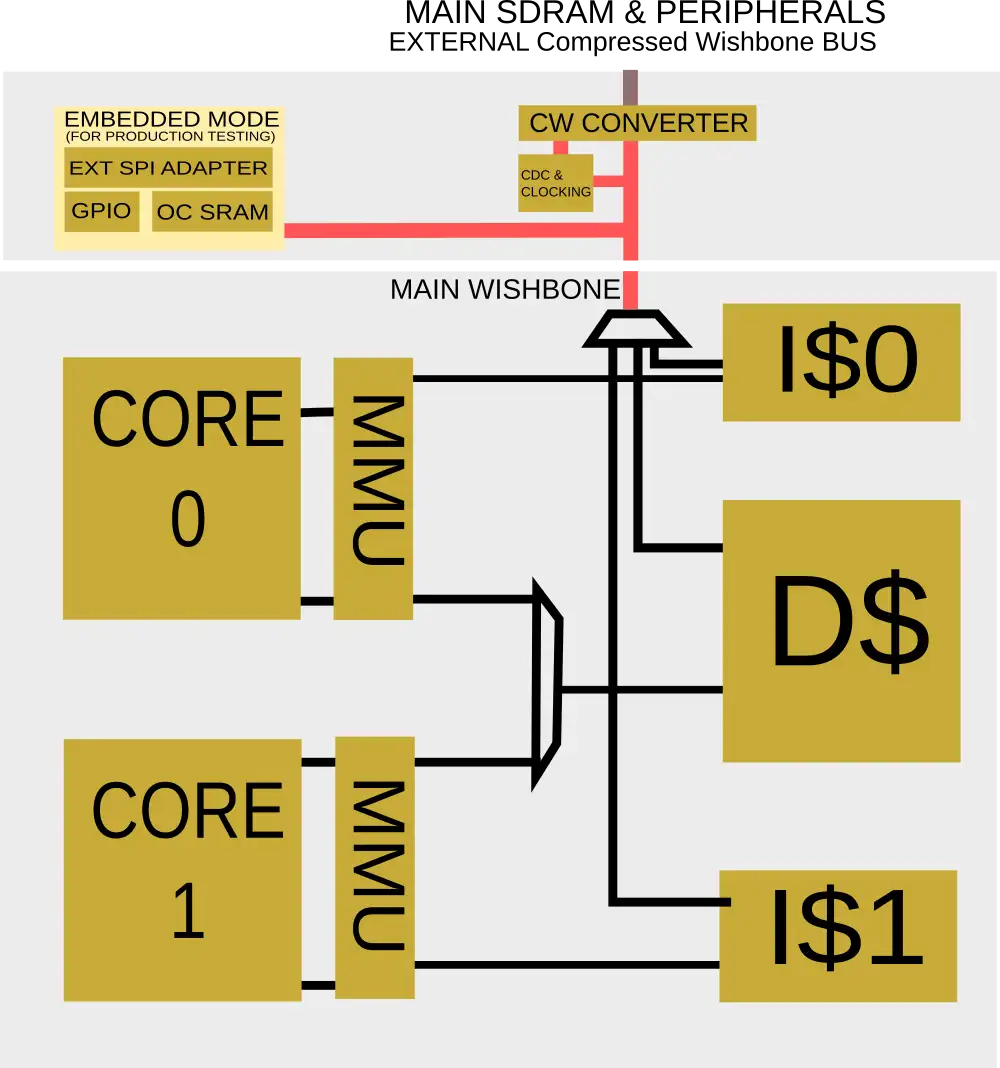

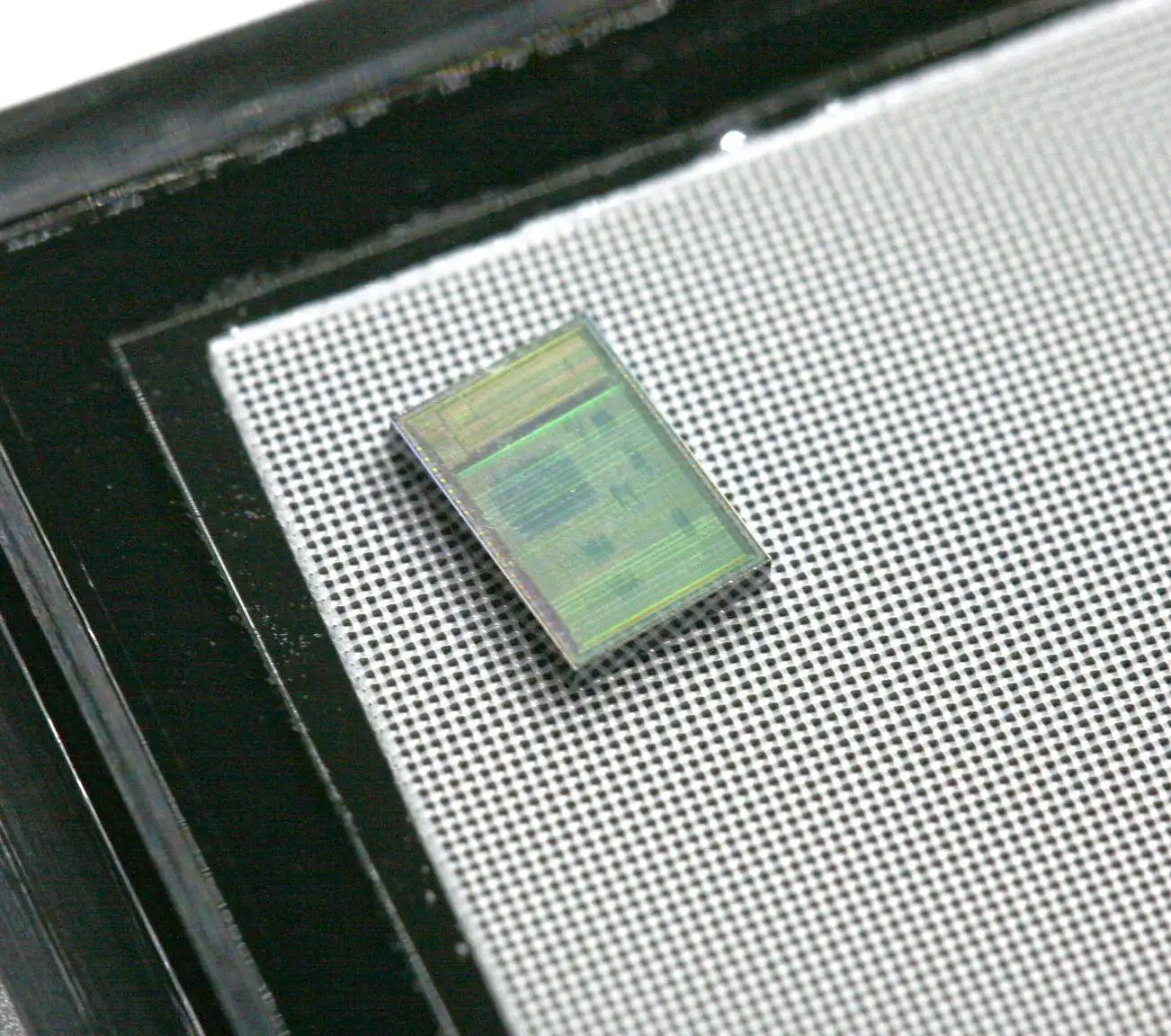

PPCPU was manufactured on Silicon on both 180nm and 130nm processes, using open source OpenLane flow. I got it from the OpenMPW shuttle program (Thanks!).

The manufactured part is the outer-level processor (including two PPCPU cores, MMUs, I/D caches, and interconnects). It can execute code from small internal memory, which is programmable externally via SPI bridge or connected via full CW (Compressed Wishone, to fit with limited I/O pins) systems bus to an external FPGA providing hardware drivers for larger memory and peripherals.

I got the first IC manufactured and tested, and not everything is working. To be precise all the LOAD and STORE instructions...

Sadly, a processor with side effects is not a very useful one, but wait a moment - is it really without side effects??? NO!

I was able to confirm that all other instructions work correctly after monitoring the system bus activity, after injecting conditional jumps and watching for change in addresses fetched by the instruction cache. You could even emulate load and stores with that setup (if you would be really desperate...).

And the second IC design should be on the way soon.

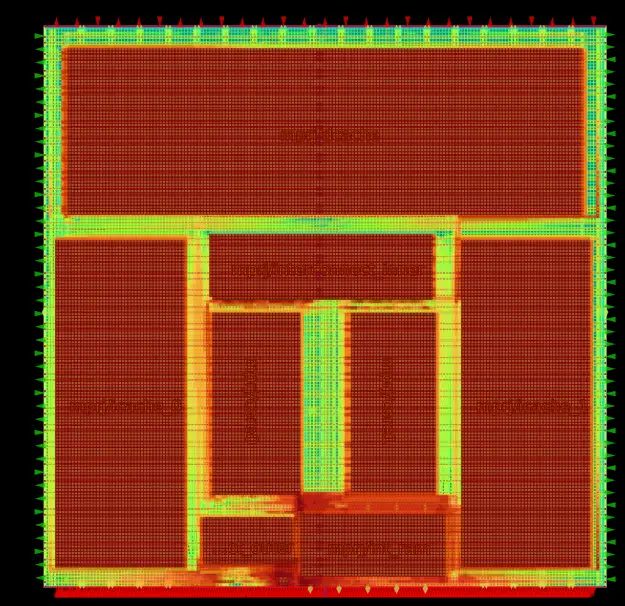

Enjoy some nice pictures while I'm working on the blog post for this very interesting, but difficult and not popular topic of designing ASICs from beginner level. and 2nd IC testing results

PPCPU silicon tape-out routing congestion diagram. (From top to bottom, then side to center: Data Cache, Instruction Cache (x2), Inner Interconnect, PPCPU core (small one x2), On-Chip SRAM, Outer Interconnect)

PPCPU silicon tape-out routing congestion diagram. (From top to bottom, then side to center: Data Cache, Instruction Cache (x2), Inner Interconnect, PPCPU core (small one x2), On-Chip SRAM, Outer Interconnect)

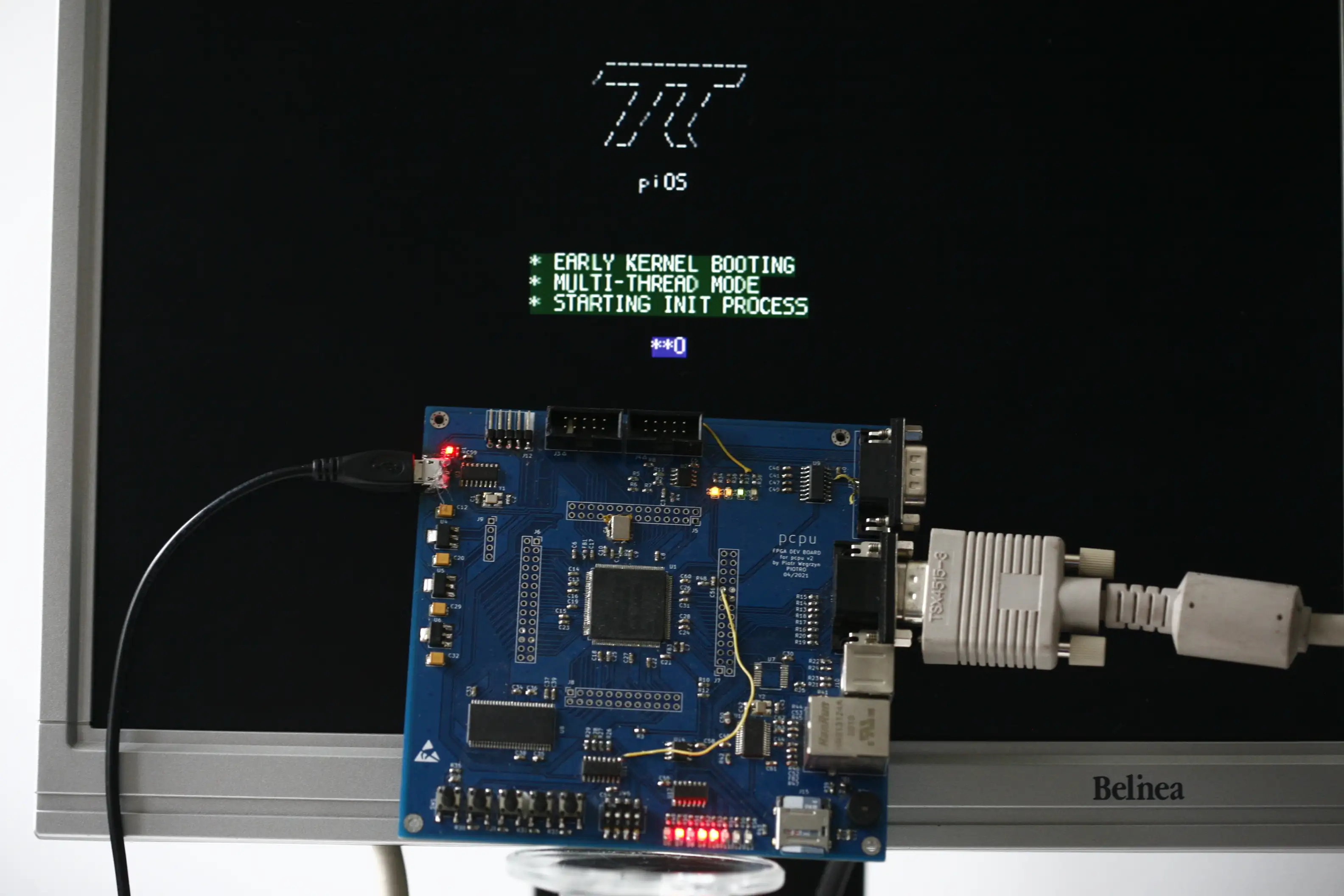

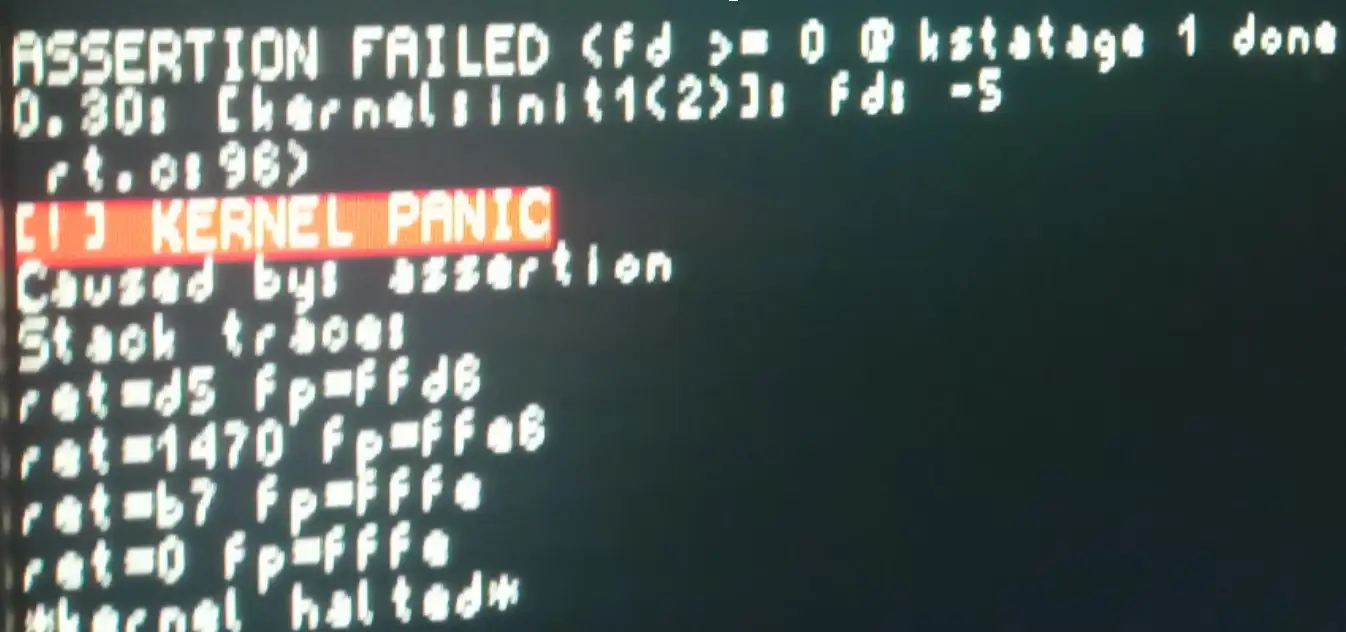

Started as some interesting demo for my processor...

and ended up as a fully featured operating system:

See piOS on GitHub

To continue work on the project, after a long journey with porting gcc and working with it (on piOS) wrapped in multiple glue logic scripts, I felt like it should be done properly this time.

In 3 months, I managed to create a complete LLVM backend for my ISA. Ported projects also include clang frontend (currently only C is supported), lld linker, and binary utilities. → This is a complete toolchain!

Check it out with build instructions on GitHub

Awesome RISC-V Out-of-Order processor generator, created with Kuźnia Rdzeni (Coreforge) research group!

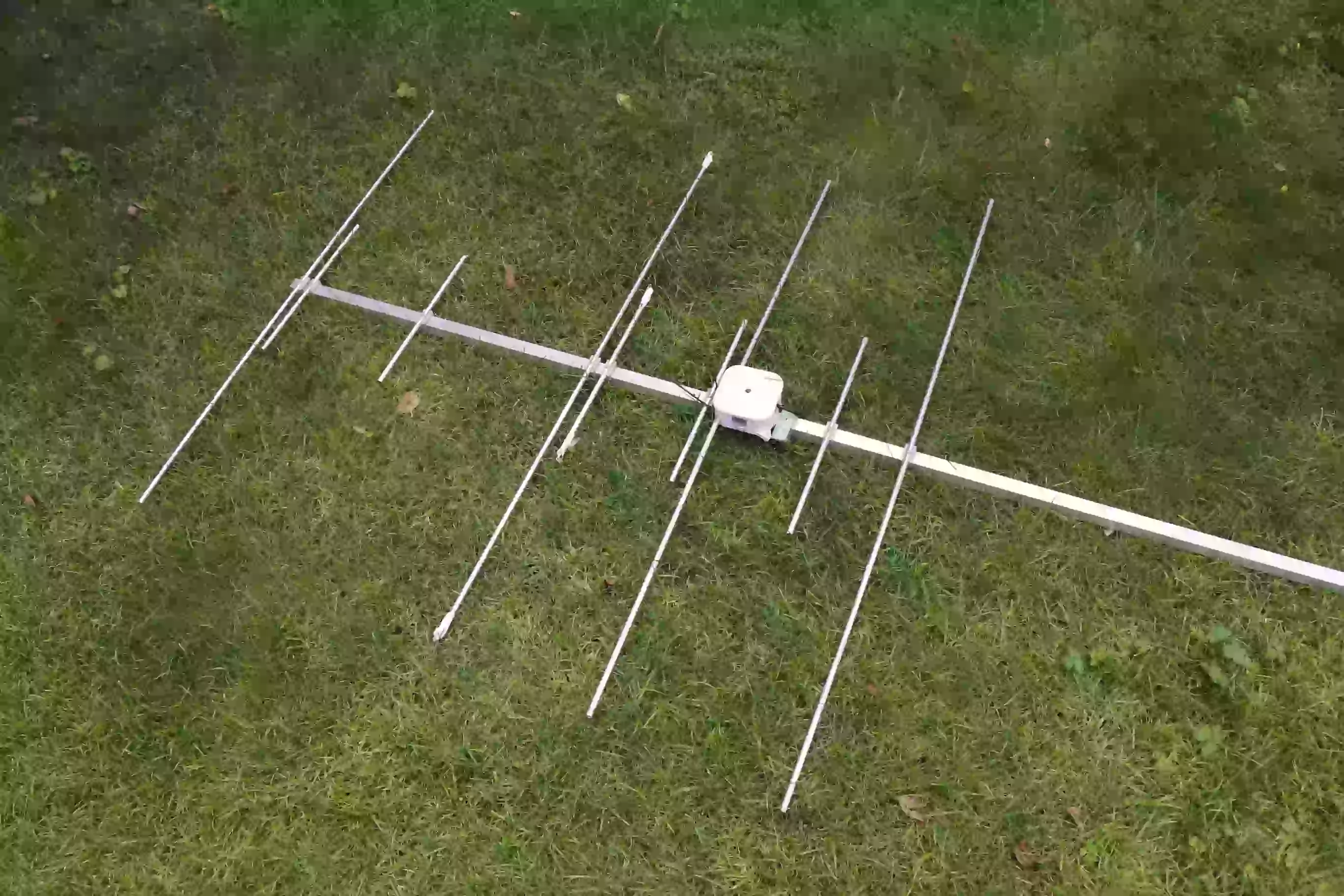

Read more about it and my work on this project in the research section or check it out on GitHubHave you ever dreamed of free dev boards falling from the sky? Look no further - meteorological departments send single-use ones up in the sky every day. Those are commonly known as radiosondes.

There are dedicated radio receiver networks, maintained by volunteers, to track and predict landing locations of sondes. That makes it a great terrain game!

I made an app to help track them in low-internet and mobile terrain conditions, combing data from two online sources, and your local radio receiver, all on one screen

I also wrote custom STM firmware, to re-use the sondes as radio beacons (on licensed amateur band) and C++ FSK transmission decoder from raw audio frames.

Source and .apk releases are available at GitHub. You can also support me by purchasing the app on Google Play

(Not finished). Hardware "framework" for creating network applications. Works by providing a common protocol parsing pipeline for incoming packets, that user modules can register to with specified filters. If decoded protocol fields are matched to the filter of the attached user sink moudules, then packet is delegated for processing to the highest priority sink. Sink modules can quickly modify the packet and resend it, or drop the packet and generate and send a new one in response.

Interesting examples shipped with the project:

(Ab)using linux apis to create a sandbox with instrumentation for automatic judging of competitive programming solutions

GitHub

DIY 40% ortho planck keyboard, I use it as my main keyboard, and it is great!

Designed PCB for it, layouts, and the 3D printed enclosure. Colemak gang btw.

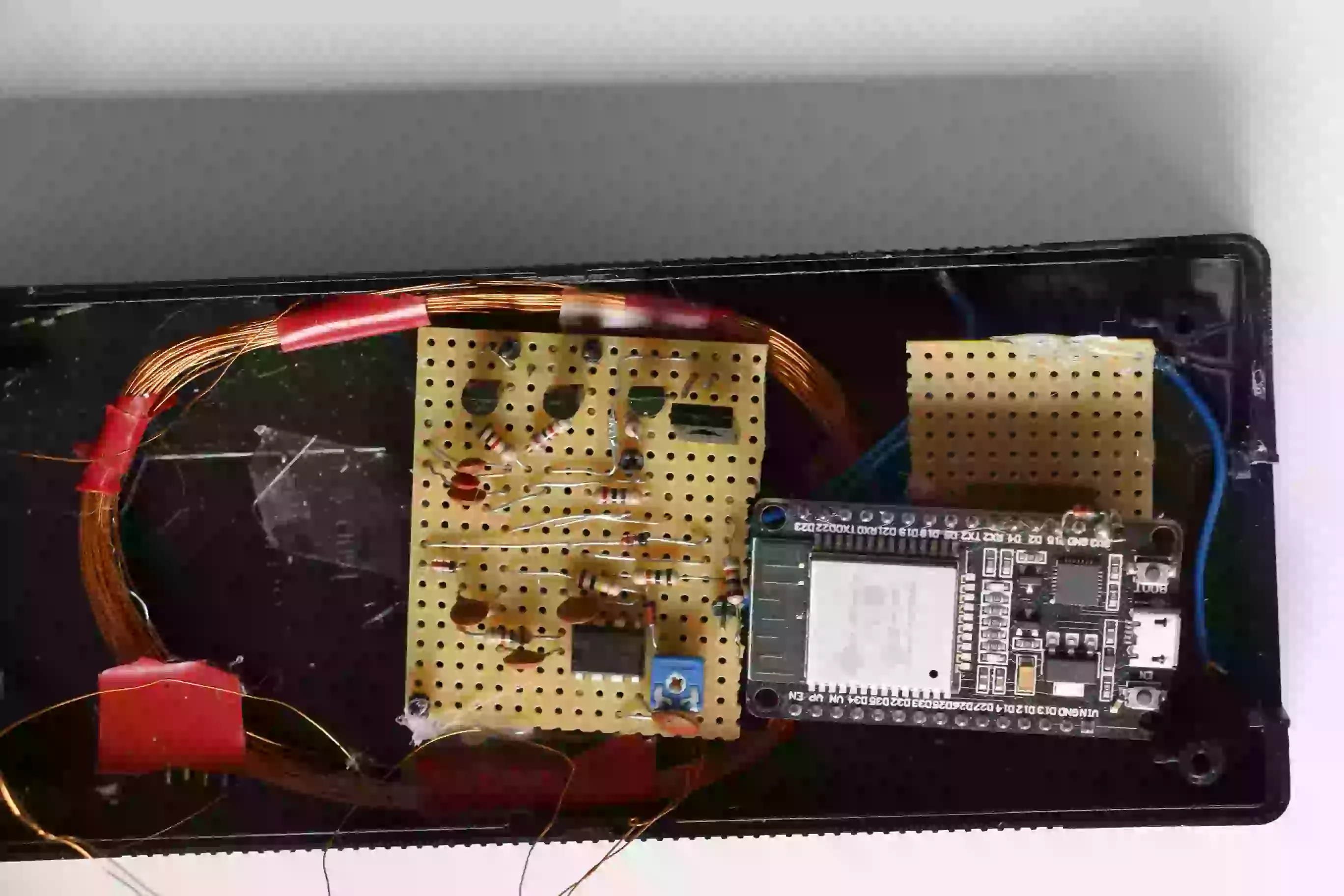

Who needs RFID modules anyway?

With a fully analog frontend, producing an output signal sampled by a single digital pin on an ESP32 microcontroller. RFID decoding is handled in ESP32, with a bluetooth serial-console interface.

[Software defined radio] Experiment to try creating SDR radio on the most basic level.

On the picture: discrete diode ring mixer, single-transistor amplifier, output opamp and some filtering. It is connected to STM32, feeding ADC samples directly to the computer, pushing the built-in USB CDC transfer to the limit. The data is converted by a python script to network format that is readable with GQRX software (~200kHz bandwidth)

When measuring the frontend on the bench I almost decided to trash it, but finally I gave it a shot. Believe it or not, it worked (first try)! It received Radio Romania Internationale and even Polish language transmission from China Radio International.

//TODO: blog post pending

Trackball made from an off-the-shelf mouse, some 3D printing, a bilard ball, keyboard switches, and a lot of hacky wires

It has a unique, accidentally invented button layout, that I find very comfortable

The goal of the project was to not modify any software (at mouse level) this time - everything is remapped with libinput settings

Turned out way better than I expected!